### SD NAND 应用存储功能描述（3）总线信号电压和时序

母线信号电压切换顺序：

初始化顺序电压切换命令顺序如下方图所示，

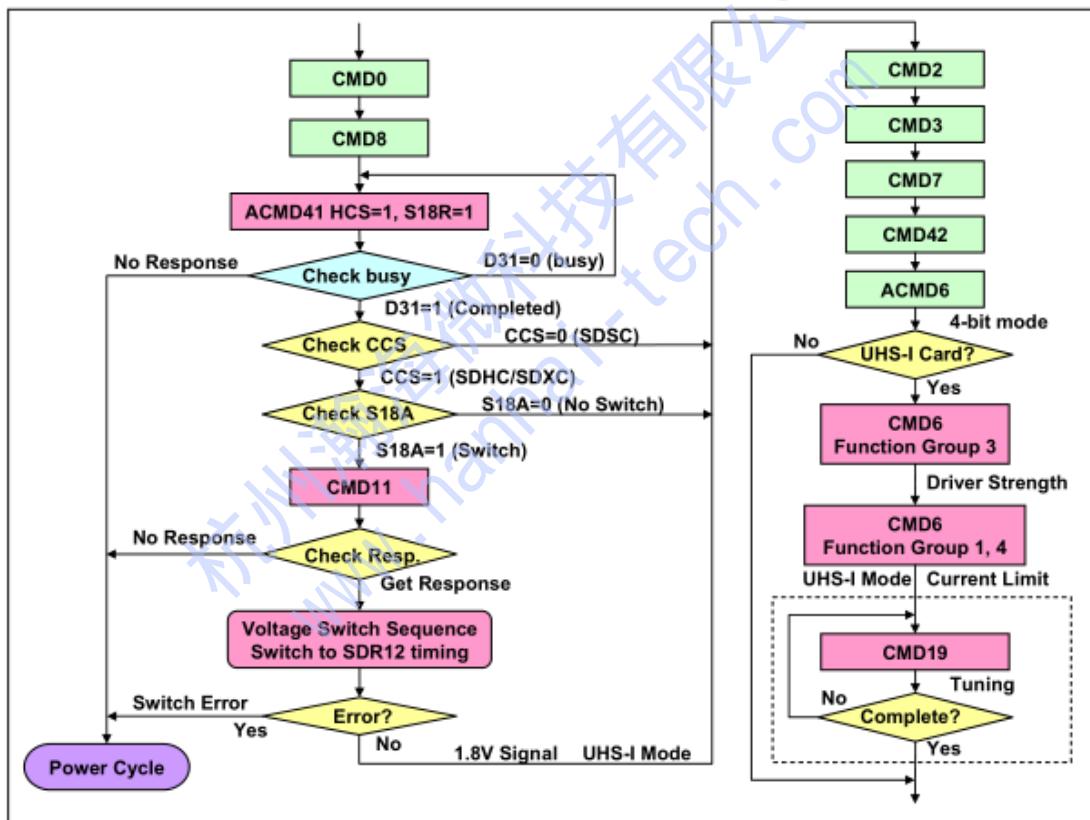

初始化命令顺序如图所示 UHS-I 主机流程图。

红色和黄色框是初始化 UHS-I 卡的新程序。

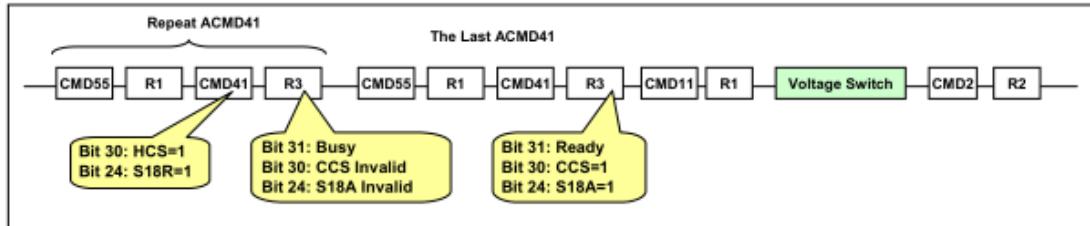

ACMD41 Timing Followed by Voltage Switch Sequence

UHS-I Host Initialization Flow Chart

当信号电平为 3.3V 时，主机重复用 HCS=1 和 S18R=1 发出 ACMD41，直到响应就绪。第一个 ACMD41 的参数(HCS 和 S18R)是有效的，但所有后续的 ACMD41 都应该使用相同的参数发布。

如果“Bit 31”表示“ready”，则主机需要检查 cc 和 S18A。

卡指示 S18A=0，表示不允许电压开关，主机需要使用电流信号电平。

卡指示 S18A=1，表示允许电压开关，主机发出 CMD11 调用电压开关序列。

通过接收 CMD11，卡返回 R1 响应并启动电压开关顺序。

CMD11 没有响应，说明 S18A 为 0，主机不应该发送 CMD11。

通过高电平 DAT[3:0]检查电压开关顺序是否完成。

DAT[3:0]的任何位都可以被检查，这取决于主机的能力。当进入 tran 状态时，需要检查 R1 响应中的 CARD\_IS\_LOCKED 状态(在 CMD7 的响应中表示)。如果卡被锁定，需要使用 CMD42 解锁卡。如果卡已解锁，则可以跳过 CMD42。

对于 UHS-I 卡，CMD6 功能组 3 选择合适的驱动强度，CMD6 功能组 1 选择其中一种 UHS-I 模式。在 SDR50 和 SDR104 模式下，如果需要对采样点进行调优，则重复下发 CMD19，直到调优完成。

### 开关信号电压定时

初始化过程中时钟频率范围为 100KHz-400KHz。下方图表显示了 ACMD41 开关信号电压的命令(S18R)-响应(S18A)组合。S18R 在命令参数中定义，表示主机的信号电压开关请求。响应中定义了 S18A，表示卡接受电压切换(这里没有切换电压)。如果信号电平已经是 1.8V，则忽略 S18R，不启动信号电压切换顺序。S18A=0 表示维持当前信令电平。

| Current Signaling Level | S18R | S18A | Comment                                  |

|-------------------------|------|------|------------------------------------------|

| 3.3V                    | 0    | 0    | 1.8V signaling is not requested          |

|                         | 1    | 0    | The card does not support 1.8V signaling |

|                         | 1    | 1    | Start signal voltage switch sequence     |

| 1.8V                    | X    | 0    | Already switched to 1.8V                 |

### S18R and S18A Combinations

通过 CMD11 调用，可以同时改变电压电平，如下图所示。CMD11 仅在响应 ACMD41 中的 S18A-1 时发布。

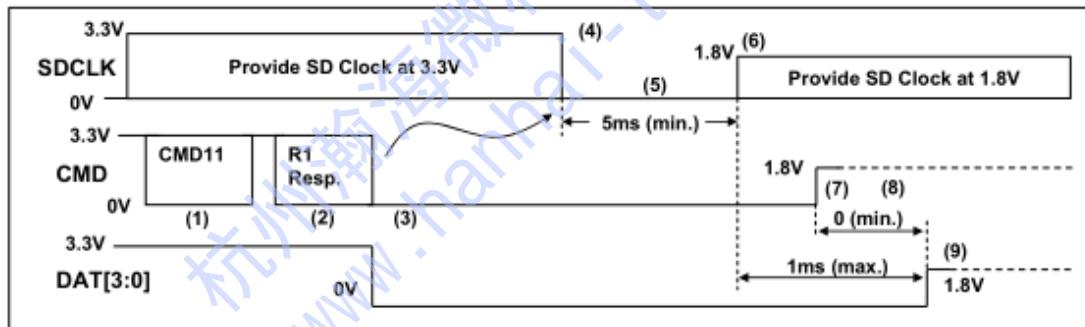

### Signal Voltage Switch Sequence

(1) 主机发出 CMD11 启动电压开关顺序。

(2) 卡返回 R1 响应(3)响应后，卡立即将 CMD 和 DAT[3:0]驱动到低电平。

(4) 主机停止提供 SDCLK。主机停止 SDCLK 后，卡开始开关电压。没有指定停止 SDCLK 的时间。

主机可以通过检查 CMD 的信号电平来检测序列是否开始，DAT(3:0)。应该检查哪个信号取决于主机的能力。如果低电平不是检测到，主机应中止该顺序并执行电源循环。

(5) 卡内稳压器 1.8V 输出在 5ms 内稳定。主机至少保持 SDCLK 较低 5 女士。这意味着 5ms 是卡的最大值，主机的最小值。

(6) 5ms 后从(4)开始，主机稳压稳定后，主机开始提供 1.8V 的 SDCLK。卡可以检查 SDCLK 电压是否为 1.8V。

(7) 通过检测 SDCLK，卡驱动 CMD 到 1.8V 高电平至少一个时钟，然后停止驱动(三态)。CMD 由 SDCLK 上升沿触发(SDR 时序)。

(8)卡可以通过主机上拉电阻检测主机是否驱动 CMD 到 1.8V。

(9)如果切换到 1.8V 信令成功完成，卡将 DAT[3:0]驱动到 1.8V 高电平至少一个时钟，然后停止驱动(tri-state)。DAT[3:0]由 SDCLK 上升沿触发(SDR 时序)。DAT[3:0]在提供 SDCLK 开始后的 1ms 内必须是高的。主机在提供 SDCLK 1 毫秒后检查 DAT[3:0]是否高。这意味着 1ms 是卡的最大值，主机的最小值。

周期(5)前后提供 3.3V 或 1.8V 的 SD 时钟，频率为 100KHz~400KHz。停止时钟只允许在(5)期间的电压切换程序。序列完成后，主机和卡在 SDR12 定时开始通信。

### 电压开关检错

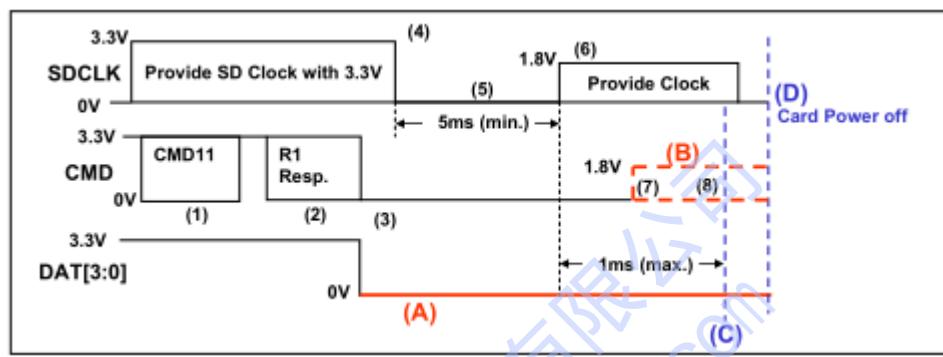

信号电压切换顺序出错时的时序如下图所示。

Error Indication Timing

(1)如果卡在(5)-(8)中检测到电压错误，卡将继续驱动 DAT[3:0]到低电平，直到卡断电。

(2) CMD 可能是低状态或三状态。

(3)主机在开始提供 SDCLK 1ms 后检查 DAT[3:0]是否高。

(4)如果 DAT[3:0]低，主机驱动 SDCLK 到低，然后停止给卡供电。

卡应检查自身稳压器输出电压和主机信号小于 2.5V。错误发生由(A)和(B)表示。